新疆网站备案校园推广方案

资料地址

兆易创新GigaDevice-资料下载兆易创新GD32 MCU

ADC简介

- ADC转换包括采样、保持、量化、编码四个步骤。

- 的采样电容上,即在采样开关 SW 关闭的过程中,外部输入信号通过外部的输入电阻 RAIN 和以及 ADC 采样电阻 RADC 对采样电容 CADC 充电。采样阶段需要在规定的采样时间内将外部信号的电压完整无误的采样到 ADC。Vref+需要在量化的过程中保持稳定。

- ADC的性能指标一般分为" 静态性能参数 "和" 动态性能参数 "

每次采样过程可以简化为:外部信号通过输入阻抗以及采样电阻对采样电容的充电电阻对采样电容的充电(即采样电容零状态的单位阶跃响应)。

误差

- 以下几种就是静态性能参数。

- 采样时间结束后,采样误差表示为采样电容上的电压与信号源上的电压差值。在一次理想的采样过程中,这个电压差值应该保持在0.5LSB以内(LSB为逐次逼近型ADC(SAR ADC)的最小电压分辨率,0.5LSB为SAR ADC的量化误差)。

偏置误差

增益误差

微分非线性误差

积分非线性误差

ADC采样信号FFT频谱图

以下就是ADC采样的动态性能参数。

信噪比(SNR)

信纳比(SNDR)

有效位数(ENOB)

总谐波系数(THD)

采样周期Ts与外部输入电阻Rain

此处仅说结论,推导过程可以在资料中找到!

故在设计SAR ADC的外围电路时,首先就要考虑其采样时间Ts和外部信号源内阻,如果忽略这些基本参数,那么采样结果很难达到理想的精度。

RC滤波与采样

此处仅说结论,推导过程可以在资料中找到!

提高精度的几种方法和注意事项

MUC供电电源

- 一般的的单片机内部都会有一个精准的内部参考源(典型电压2.5V),可以用作ADC工作时的电压,该内部参考电压可以连接到Vref引脚上,但是需要注意的是,其内部参考源带载能力不强,谨慎选择所带负载大小。

- 量化编码过程中,Vref+需要给转化电容网络充电在量化过程中,也会有对基准源抽 取电荷的作,因此,如果没有其他的去耦措施,一个稳健且干净的 Vref+基准会显著影响 ADC 量化的精度,建议对于这两个电源采用纹波噪声系数更小的 LDO 来供电。

- 对于 VREF+基准源,建议靠近引脚并联一个 uF 级以及一个 nF 级的去耦电容,一方面可以滤除来自外部低频与高频的电源噪声,另一方面,也可使 ADC 在量化编码过程的基准源更加稳定。

- 在 layout 过程中,相关电源线的走线上,推荐加宽电源迹线,以减小迹线的 ESR,在量化阶段,减小转化电容网络瞬间充电对输入基准源的影响。

引脚电容

参考电压设置

采样信号的幅值不应超出 VREF+的幅值,对于无VREF+引脚的 MCU,采样信号的幅值不应超出 VDDA 的幅值,否则可能会导致模拟电源漏电,严重影响 ADC 性能。

IO口引入超范围电压

信号源输入电阻的影响

当信号源输入电阻不满足要求

假设锂电池的电压为24V,用R1=9MΩ、R2=1MΩ的电阻分压,然后将分压结果送进ADC通道进行采样,其并联得到的输出阻抗为0.9MΩ。

改善方法

- 添加一个运放跟随电路,实现阻抗匹配。

- 如果对于采样率没有要求的情况下,我们可以降低 ADC 的采样时钟,变相提高采样时间来使 得采样电容充电到正确电位。

- 在功耗要求可以放宽时,我们可以同比例缩小 R1,R2 两个电阻,比如 R1=900k,R2=100k,此时该分压电路的输出阻抗变为90k,配置合适的采样周期,已经能够满足ADC的阻抗要求。

保证ADC采样精度的改善方法

对于 SAR ADC 在采样时间内,采样电容上的电压必须被充分充放电,其被 充电的电压值与外部输入电压之间的差值不应超过 0.5LSB ,否则无论后级 ADC 性能如何卓 越,都无法真实反映信号的幅值。

- 对于极大输入阻抗,我们添加了一颗电容来限制单次采样时的电压跌落或上升毛刺的幅值,但是此种情形下,需要在每两次采样之间添加足够的时延给内部采样电容充电,以保证采样开关关闭时,采样电容上的电压与外部信号的电压差在量化误差范围一列。

- 当 ADC 工作在连续采样或者扫描采样时,如果由于输入阻抗过大,且未被及时修正时,输入阻抗过大通道的采样结果会受前一个采样通道信号的影响,通过增大采样时间以满足输入阻抗的影响会显著改善这个现象。

I/O引脚串扰

- 在引脚规划上,就需要提前规划将那些需要持续翻转的数字 I/O 在物理位置上远离 ADC 采样通道。

- 如果由于资源限制,频繁翻转的数字 I/O 无法远离模拟采样口,我们可以在后期 layout 上采取一些措施来减弱影响,比如我们可以通过在数字 I/O 与模拟通道之间加上一定面积的 GND 来隔离。

- 此外,减慢数字信号的边沿也会减弱串扰的影响,如对数字信号添加电容值适当的电容,减慢 MCU 数字 IO 口的驱动速度,也能显著减慢这个数字信号边沿。

- 在数字 I/O 口不翻转的时候进行一次 ADC 转换,当然前提是应用允许这么做。

软件提高ADC采样精度

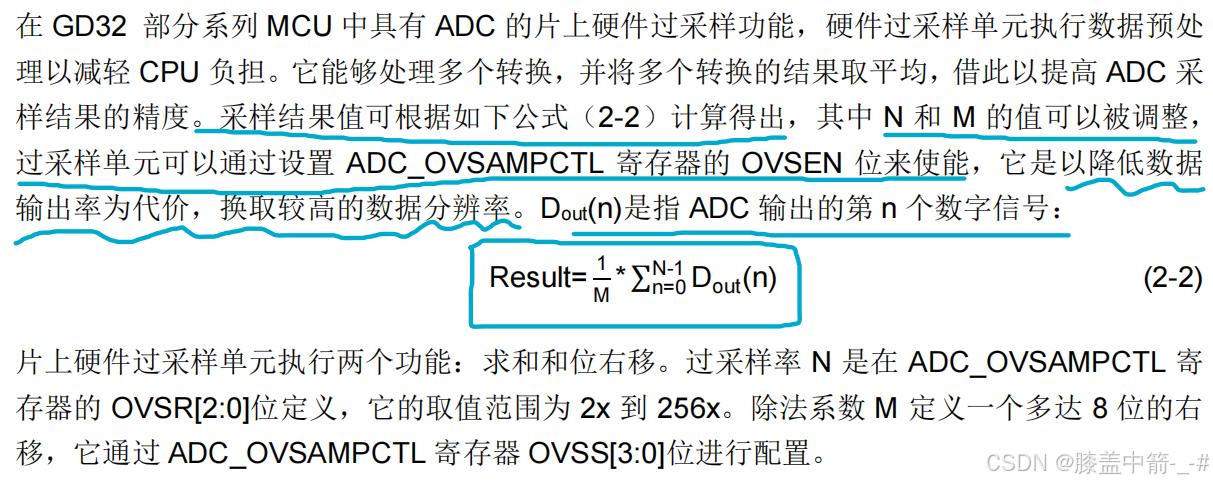

- 使用ADC片上硬件过采样。

- 不具备片上硬件过采样单元的 MCU,软件算法上亦可采用常用的一些滤波算法来降低输入信号采样值的波动。例如最常见的平均算法,滤波过程中需要占用CPU的算力与一定的RAM空间。这种平均算法适用于输入信号变化慢,偶有脉冲型干扰的情形。如果信号变化频率已经大于这个平均滤波算法的执行频率,则会丢失信号变化的细节,平均后的采样结果不能重现信号的所有信息。此平均算法一般只用于采样直流小信号,不建议用于采样交流连续信号(例如正弦波等等)。