安丘网站建设郑州靠谱seo整站优化

文章目录

- 一、概述

- 1.异步时序

- 2.亚稳态与建立保持时间

- 二、跨时钟域处理

- 1.控制信号的跨时钟域处理(单bit数据)

- a.慢时钟域到快时钟域

- b.快时钟域到慢时钟域

- 握手“扩宽”快时钟域脉冲

- 时钟停止法

- 窄脉冲捕捉电路

- 2.数据信号的跨时钟域处理(多bit数据)

- (1)开环结绳法(脉冲同步)

- (2)闭环结绳法

- (3)异步FIFO(推荐使用)

一、概述

1.异步时序

异步时序就是一个设计中有多个时钟,每个时钟的源头不一样,即:多个时钟之间无确定性关系,称为异步时序

2.亚稳态与建立保持时间

建立时间:在时钟有效沿到达之前数据保持稳定的时间

保持时间:在时钟有效沿到达之后数据保持稳定的时间

(为啥有建立保持时间要求见:寄存器为什么有建立保持时间要求)

建立时间和保持时间组成时间窗,如果信号在这个时间窗中间发生变化,则信号有效沿采样数据得到的结果是不可预知的,即亚稳态。

亚稳态:指触发器无法在某个规定的时间段内达到一个确定的状态,介于0和1之间。亚稳态是可以传输的,导致逻辑误判系统不稳定。亚稳态是无法消除的,只能被降低。

二、跨时钟域处理

1.控制信号的跨时钟域处理(单bit数据)

a.慢时钟域到快时钟域

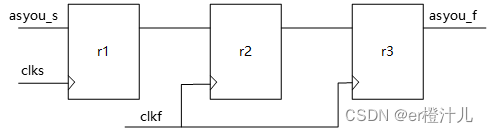

这里的慢时钟域到快时钟域,需要满足:目标时钟频率必须是源时钟频率1.5倍及以上,才能算慢时钟域到快时钟域。这种情况下只需要考虑跨时钟域的情况,一般根据电路的工作频率,芯片所采用的工艺,决定打2拍或3拍,即常规的同步寄存器。电路图如下:(这里以2拍寄存器为例)

b.快时钟域到慢时钟域

注:目标时钟频率是源时钟频率的1~1.5倍,还是按照“快时钟域到慢时钟域”的方法来处理,目的是为了保险起见

快时钟域到慢时钟域除了要处理亚稳态问题,还要防止漏采,因为如果是快时钟域中的单脉冲信号,那么慢时钟域可能无法采样到该信号

握手“扩宽”快时钟域脉冲

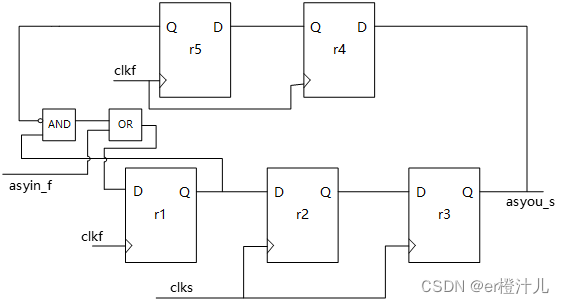

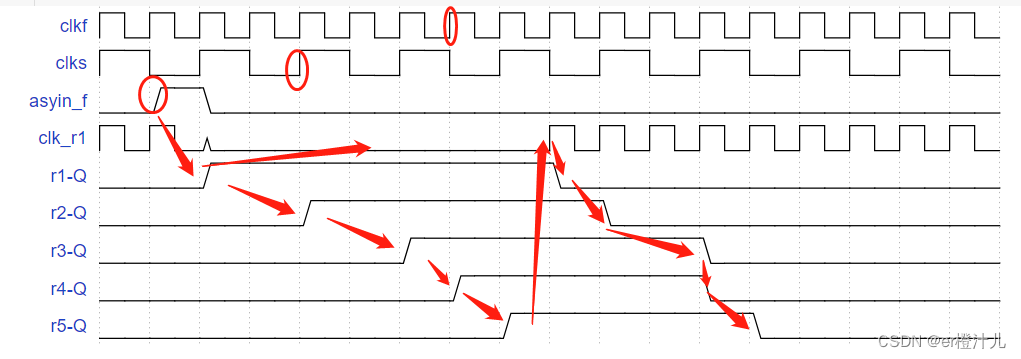

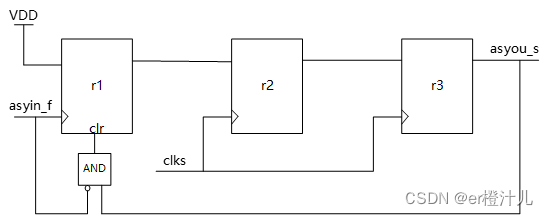

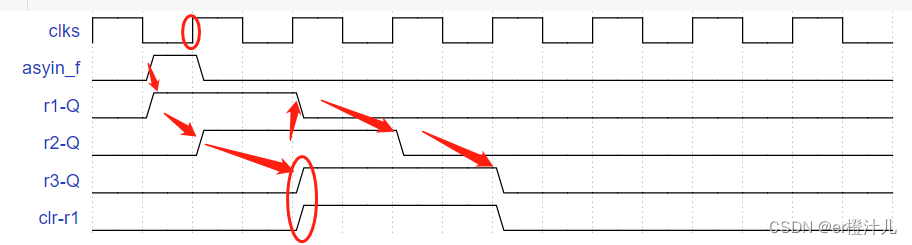

如图所示:clkf为快时钟域,clks为慢时钟域。快时钟域信号asyin_f经过寄存器r1,穿到慢时钟域,经过r2,r3两级寄存器打拍后反馈回快时钟域,r1的输入在接收到反馈回的信号之后才拉低,通过“握手”实现asyin_f信号的扩宽,时序图如下所示:

如图所示:clkf为快时钟域,clks为慢时钟域。快时钟域信号asyin_f经过寄存器r1,穿到慢时钟域,经过r2,r3两级寄存器打拍后反馈回快时钟域,r1的输入在接收到反馈回的信号之后才拉低,通过“握手”实现asyin_f信号的扩宽,时序图如下所示:

时钟停止法

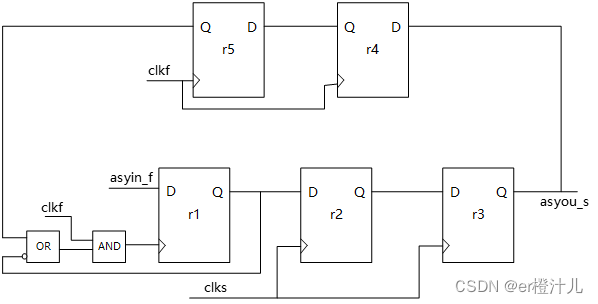

如图所示,时钟停止法与握手法类似,都是快时钟域信号到慢时钟域被正确采样后,反馈回快时钟域。只是时钟停止法,是通过在异步信号到来之后,将r1的输出拉高之后将r1的时钟停掉,这时由于时钟下一个有效沿未到达,r1寄存器的输出保持高电平不变,直到慢时钟域的信号反馈回来之后,r1寄存器的时钟才开始正确翻转,r1寄存器的输出才更新。通过这种方法也能扩宽asyin_f信号,保证其能正确被慢时钟域采样,时序图如下所示:

窄脉冲捕捉电路

这种方法比上面两种方法更节约寄存器资源,该方法通过异步脉冲信号驱动寄存器r1输出拉高,当r1为高之后,asyin_f已经停止(单脉冲),因此寄存器r1的输出保持为高不斌,然后等待慢时钟域信号拉低寄存器r1的输出(clr信号,高电平有效),时序图如下所示:

注:上面三种方法中,第二种和第三种方法都会对寄存器时钟进行操作,在实际设计中需要综合考虑。

2.数据信号的跨时钟域处理(多bit数据)

(1)开环结绳法(脉冲同步)

开环结绳的方法:

• 在一个数据的起始端和结束端,发送两个脉冲(clka时钟域)

• 第一个脉冲来,就hold一个信号,直到第二个脉冲到来,把hold信号拉低(hold_clka)

• 在clkb时钟域采样hold_clka信号,得到hold_clkb

• 将hold_clkb恢复成两个脉冲,根据这两个脉冲来采样clka时钟域的数据

(2)闭环结绳法

闭环结绳的方法:

• 在数据起始端,clka拉起hold,为hold_clka

• clkb采样hold_clka,得到hold_clkb,恢复为一个脉冲,对该数据采样,反馈该脉冲到clka

• clka得到该脉冲,拉低hold_clka;同步到clkb,拉低hold_clkb

(3)异步FIFO(推荐使用)

异步FIFO的设计见 Verilog实现异步FIFO&异步FIFO常见问题集锦