深圳高端网站建设公司百度提交入口网址

目录

一:时钟控制

1:基本概念

2:时钟结构图

3:结构图分析

4:总线

5:寄存器

A:FCLK--MPLLCON

B:HCLK和PCLK--CLKDIVN

C:注意

二:上电复位

1:上电复位

2:时钟选择

三:代码

一:时钟控制

1:基本概念

S3C2440A中的时钟控制逻辑可以产生所需的时钟信号,包括CPU的FCLK、AHB总线外设的HCLK和APB总线外设的PCLK。S3C2440A具有两个锁相环(pll):一个用于FCLK,HCLK和PCLK, 另一个专用于USB块(48Mhz)。时钟控制逻辑可以制作无锁相环的慢时钟,并通过软件将时钟连接断开到各个外设块,从而降低功耗。

对于电源控制逻辑,S3C2440A具有多种电源管理方案,以保持给定任务的最佳功耗。S3C2440A的电源管理模块可以激活四种模式:NORMAL模式、SLOW模式、IDLE模式和SLEEP模式。

NORMAL模式:该模块为CPU以及S3C2440A中的所有外设提供时钟。在此模式下,当所有外设都打开时,功耗将达到最大。它允许用户通过软件控制外设的操作。例如,如果不需要定时器,用户可以断开时钟(CLKCON寄存器)对定时器的连接,以减少功耗。

SLOW mode:非pll模式。与正常模式不同,慢速模式在S3C2440A中直接使用外部时钟(XTipll或EXTCLK)作为FCLK,没有PLL。在这种模式下,功耗仅取决于外部时钟的频率。不包括PLL的功耗。

IDLE模式:块只断开CPU核心的时钟(FCLK),而它向所有其他外设提供时钟。IDLE模式可以降低CPU核的功耗。任何对CPU的中断请求都可以从空闲模式唤醒。

SLEEP模式:模块断开内部电源。因此,在这种模式下,除了唤醒逻辑外,不会发生CPU和内部逻辑的功耗。激活SLEEP模式需要两个独立的电源。其中一个电源为唤醒逻辑提供电源。另一个提供包括CPU在内的其他内部逻辑,并且应该控制电源的开/关。在SLEEP模式下,CPU和内部逻辑的第二电源将关闭。从SLEEP模式唤醒可以由EINT[15:0]或RTC告警中断发出。

2:时钟结构图

主时钟源 : 来自外部晶体(XTip12MHz) 或外部时钟(EXTCLK)。时钟发生器包括一个振荡器(振荡放大器),它连接到外部晶体,也有两个锁相环(锁相环),它产生S3C2440A所需的高频时钟。

FCLK: 直接挂载在ARM芯片上面---400MHZ

HCLK------挂载在AHB总线上(高速总线)====>挂载了nand flash , LCD控制, USB, 电源管理等外设----136MHZ

PCLK-----挂载在APB总线上(低速总线)======>挂载了I2c, ADC, PWM等外设----68MHZ

CLKCNTL---是一个控制寄存器,用于控制系统时钟的分频和选择。它可以生成FCLK,然后通过HDIVN和PDIVN分频得到HCLK和PCLK。其中,FCLK传递给CPU,HCLK和PCLK用于其他外设

3:结构图分析

晶振-----选择器-----PLL锁相环(MPLL和UPLL)具体内容见1------HCLK和PCLK分别挂载在AHB总线和APB总线上面-----在线上面又挂载了许多外设

1: 晶振经过锁相环, 在经过FCLK处理完的晶振频率直接给到ARM芯片(CPU); FCLK处理之后的晶振频率在经过HDIVN和PDIVN分频器的处理分别得到HCLK和PCLK ;

4:总线

时钟工作的最大频率:

5:寄存器

我们程序实现: FCLK=400MHZ HCLK=100MHZ PCLK=50MHZ

A:FCLK--MPLLCON

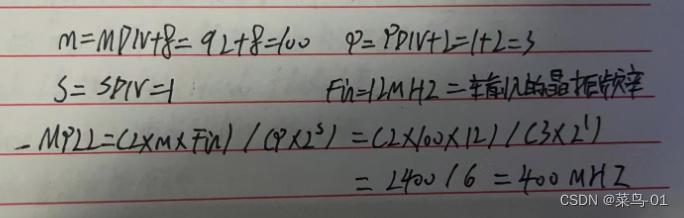

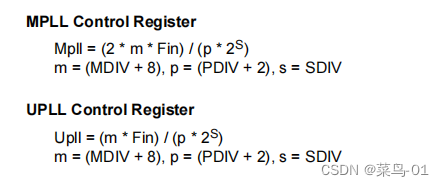

通过编辑MPLLCON寄存器的MDIV, PDIV, SDIV; 来得到FCLK相应的频率

我们看到了输入为12MHZ的晶振, 为了得到输出为400MHZ的晶振

MDIV=92(0x5c) PDIV=1 SDIV=1

公式为:

ldr r0, =0x4C000004ldr r1, =(92<<12)|(1<<4)|(1<<0)str r1, [r0]B:HCLK和PCLK--CLKDIVN

当CAMDIVN[9] = 0时, DHIVN[2:1]=10; DHIVN------400/4=100

PDIVN[0]=1--------PDIVN=100/2=50

CLKDIVN[2:0]=101=0x5

ldr r0, =0x4C000014ldr r1, =0x5str r1, [r0]不要忘记了CAMDIVN[9] = 0

我们可以看到了第9为默认为0, 但是我们为了保险设置一下

ldr r0, =0x4C000018ldr r1, =(0<<9)str r1, [r0]完整代码

ldr r0, =0x4C000018ldr r1, =(0<<9)str r1, [r0]ldr r0, =0x4C000014ldr r1, =0x5str r1, [r0]C:注意

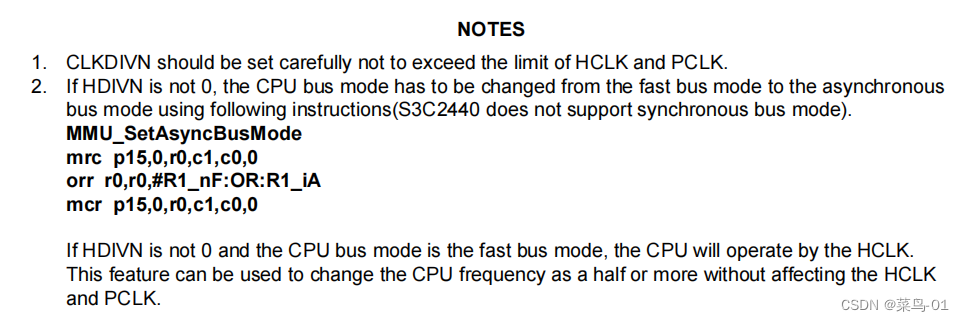

1. CLKDIVN的设置要小心,不要超过HCLK和PCLK的限制。

2. 如果HDIVN不是O,则需要按照下面的说明将CPU总线模式从快速总线模式切换到异步总线模式(S3C2440不支持同步总线模式)。

3: 当HDIVN不为0且CPU总线模式为快速总线模式时,CPU将通过HCLK工作。该特性可以在不影响HCLK和PCLK的情况下,将CPU频率改变一半或更多。

所以我们需要在异步模式下工作, 将他调节为异步模式

/* 设置CPU工作于异步模式 */mrc p15,0,r0,c1,c0,0orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iAmcr p15,0,r0,c1,c0,0二:上电复位

1:上电复位

上电复位(XTIpll)上电复位顺序的时钟行为如图所示。晶体振荡器在几毫秒内开始振荡。当OSC (XTipll)时钟稳定后释放nRESET后,PLL开始按照默认PLL配置工作。然而,PLL通常在上电复位后不稳定,因此在软件重新配置PLLCON之前,Fin直接馈送到FCLK而不是Mpll (PLL输出)。即使用户在复位后不希望改变PLLCON寄存器的默认值,用户也应该通过软件将相同的值写入PLLCON寄存器。只有软件为PLL配置了新的频率后,PLL才会向新的频率重新启动锁相序列。FCLK可以配置为锁定时间后立即PLL输出(Mpll)。

这个nRESET。这里会维持一段时间。为什么一上电的时候nRESET不能够立刻拉高呢?因为。他要维持一段时间,等待你这个电源稳定,谁来帮你维持这个nRESET这么一段时间呢?我们的二四零里面有专用的复位芯片。

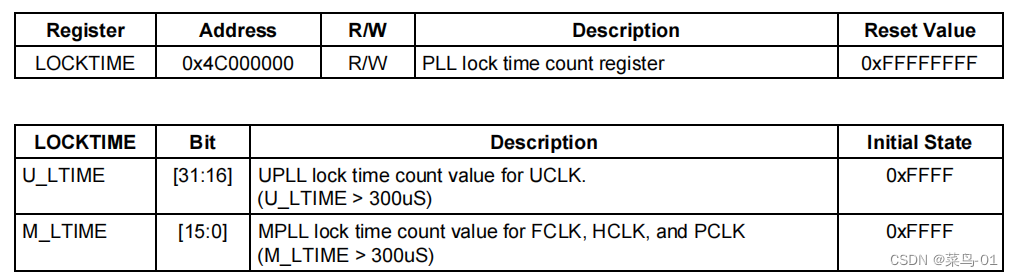

锁存时间寄存器

2:时钟选择

时钟源的选择S3C2440A的模式控制引脚(OM3和OM2)组合与源时钟选择的关系。OM[3:2]状态通过参考nRESET上升沿的OM3和OM2引脚在内部锁存。

虽然MPLL在复位后启动,但直到软件将有效设置写入MPLLCON寄存器时,MPLL输出(MPLL)才被用作系统时钟。在此有效设置之前,来自外部晶体或EXTCLK源的时钟将直接用作系统时钟。即使用户不想改变MPLLCON寄存器的默认值,用户也应该将相同的值写入MPLLCON寄存器。当OM[1:0]为11时,OM[3:2]用于确定测试模式。

三:代码

.text

.global _start_start:

/* 关闭看门狗 */ldr r0, =0x53000000ldr r1, =0str r1, [r0]/* 设置MPLL, FCLK : HCLK : PCLK = 400m : 100m : 50m *//* LOCKTIME(0x4C000000) = 0xFFFFFFFF */ldr r0, =0x4C000000ldr r1, =0xFFFFFFFFstr r1, [r0]/* CLKDIVN(0x4C000014) = 0X5, tFCLK:tHCLK:tPCLK = 1:4:8 */ldr r0, =0x4C000018ldr r1, =(0<<9)str r1, [r0]ldr r0, =0x4C000014ldr r1, =0x5str r1, [r0]/* 设置CPU工作于异步模式 */mrc p15,0,r0,c1,c0,0orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iAmcr p15,0,r0,c1,c0,0/*设置MPLLCON*/ldr r0, =0x4C000004ldr r1, =(92<<12)|(1<<4)|(1<<0)str r1, [r0]/* 一旦设置PLL, 就会锁定lock time直到PLL输出稳定* 然后CPU工作于新的频率FCLK*//*设置内存: sp栈* 我们判断是nor启动还是nand启动/mov r1, #0ldr r0, [r1] /* 读出原来的值备份 */str r1, [r1] /* 0->[0] */ ldr r2, [r1] /* r2=[0] */cmp r1, r2 /* r1==r2? 如果相等表示是NAND启动 */ldr sp, =0x40000000+4096 /* 先假设是nor启动 */moveq sp, #4096 /* nand启动 */streq r0, [r1] /* 恢复原来的值 */bl mainhalt:b halt